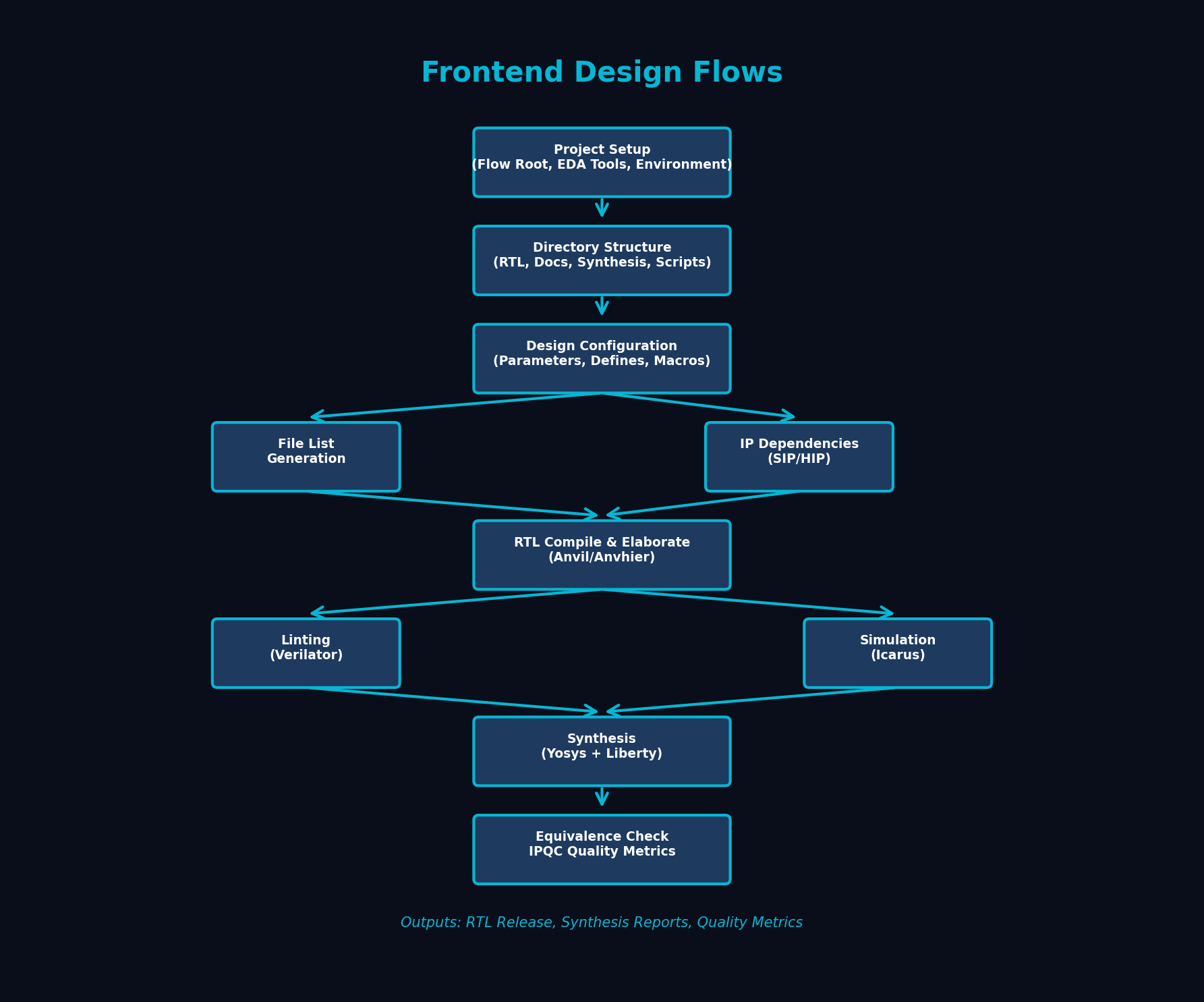

The Frontend Design Flow provides a comprehensive methodology for RTL development, from project setup through synthesis and quality checks. This flow follows industry best practices and integrates seamlessly with the EDAUtils AI System.

Flow Root Configuration: Establish FLOW_ROOT environment variable pointing to project base directory. Set EDA tool versions and licensing.

Environment Variables: Configure PATH, LD_LIBRARY_PATH, and tool-specific variables (VCS_HOME, YOSYS_PATH, etc.).

Workspace Initialization: Create standard directory tree, set permissions, initialize version control.

Generic RTL with Parameters: Write parameterizable RTL code using `parameter` and `define` macros. Example: addr_width=128, data_width=64.

Configuration Files: Maintain separate configuration files for different design variants. Use +define+ compiler directives for conditional compilation.

Parameter Overrides: Command-line parameter passing for quick design exploration. Design-time vs. compile-time parameters.

Anvil/Anvhier Tools: Fast RTL compilation and elaboration. Syntax checking, module hierarchy analysis, parameter propagation validation.

Error Detection: Catch syntax errors, undefined modules, port mismatches, width mismatches early in the flow.

Elaboration Reports: Module hierarchy tree, instance counts, parameter values, memory usage estimates.

Style Checking: Coding style violations, naming conventions, unused signals and variables.

Quality Checks: Combinational loops, inferred latches, multi-driven nets, clock domain issues.

Waiver Management: Systematic waiver of known false positives. Waiver review and audit trails.

RTL Synthesis: Yosys open-source synthesis engine. Technology mapping to ASIC or FPGA targets.

Liberty Library: Timing library (.lib) integration. Cell characterization and delay models.

Constraints: SDC (Synopsys Design Constraints) for timing. Clock definitions, input/output delays, false paths.

Reports: Area, timing, power analysis. Quality of results (QoR) metrics.

Formal Verification: Equivalence checking between RTL and synthesized netlist. Verification of design transformations.

IPQC Quality Checks: IP Quality Check automated analysis. Coverage metrics, lint clean status, synthesis QoR.

Release Criteria: Pass/fail criteria for RTL release. Quality gates and sign-off requirements.

Contact us for detailed implementation guides and support